LA 1 M2

2. Alat dan Bahan

[Kembali]

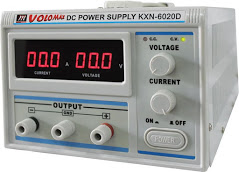

a. Jumper

Gambar 1. Jumper

3. Rangkaian Simulasi [Kembali]

4. Prinsip Kerja Rangkaian

[Kembali]

Rangkaian pada percobaan 1 ini menggunakan JK flip flop dan D flip flop yang

memiliki kesenjangan kondisi, dimana kedua input R & S pada flip flop tersebut salah satunya

aktif yang mengakibatkan tabel kebenaran untuk sekma input D J K logika rise dan fall time pada

masing-masing clock tidak berlaku atau tidak berpengaruh terhadap

rangkaian

5. Video Rangkaian

[Kembali]

6. Analisa

[Kembali]

Soal analisa :

Percobaan 1

1. Analisa apa yang terjadi saat input B3 dan

B2 dihubungkan ke Clock dan K berlogika 1

gambarkan timing diagramnya

2. Analisa apa yang terjadi saat B5 dan B6 dihubungkan ke

Clock

gambarkan timing diagramnya

Percobaan

2

1. Analisa apa yang terjadi saat B2 dan input J dan K dihubungkan ke

Clock

gambarkan timing diagramnya

Jawab :

Percobaan 1 :

1. ketika B2 dan B3 terhubung ke clock maka sistem

rangkaian akan mengalami error dan tidak dapat berfungsi dengan baik, sehingga kondisi B2 dan B3

terkoneksi menuju clock tidak mengubah output sama sekali dan saat pertukaran kondisi B2 dan B3

mengakibatkan rangkaian berada dalam kondisi tak terdefinsikan

2. D flip flop yang input nya D = 0 dan B5 dan

B6 yang terhubung ke clock mengakibatkan logika clock B5 OR B6

Percobaan 2

1. Kondisi ini mengakibatkan setiap kali input T

& CLK di ubah saat R & S non aktif (berlogika 1) maka output tidak mengalami perubahan

sama sekali

7. Link Download

[Kembali]

- Download HTML [klik disini]

- Donwload Rangkaian Simulasi [klik disini]

- Download Video Simulasi [klik disni]

- Download Datasheet ic 74LS112A [klik disini]

- Download Datasheet ic 7474 [klik disini]

.jpeg)

Komentar

Posting Komentar